Reference designs

Points to verify

- Do you wire from PERxy on the M.2 side to PERxy on the Oculink side, or PERxy to PETxy?

- Do all of the control signals need to be connected?

- Is SMB (system management bus) data and clock required or is it optional?

- What about the MFG (manufacturer) data and clock on the M.2 card which is not present on the Oculink connector or PCIe standard?

- Is lane reordering and polarity inversion okay to use for routing PCIe connections?

AdtLink M.2 to PCIe extension

Image 2. Adtlink M.2 to PCIe 4.0 adapter

(source)

[CLKREQ, PERST]are connected.[PEWAKE, PEDET]are not connected.[SMB_CLOCK, SMB_DATA]are not connected.[MFG_CLOCK, MFG_DATA]are not connected.3.3Vis connected.REFCLKis connected with same polarity.[PERxy, PETxy]lanes are connected with same polarity and same order.

GPD Win v1 M.2 to Oculink card

Image 3. GPD win 1 M.2 to Oculink adapter card

(source)

[PERST, PEDET]are connected.CLKREQis connected but through a Schottky diode.PEWAKEis not connected.[SMB_CLOCK, SMB_DATA]are not connected.[MFG_CLOCK, MFG_DATA]are not connected.3.3Vis connected through a jumper.REFCLKis connected with same polarity.[PERxy, PETxy]lanes are connected with same polarity and same order.

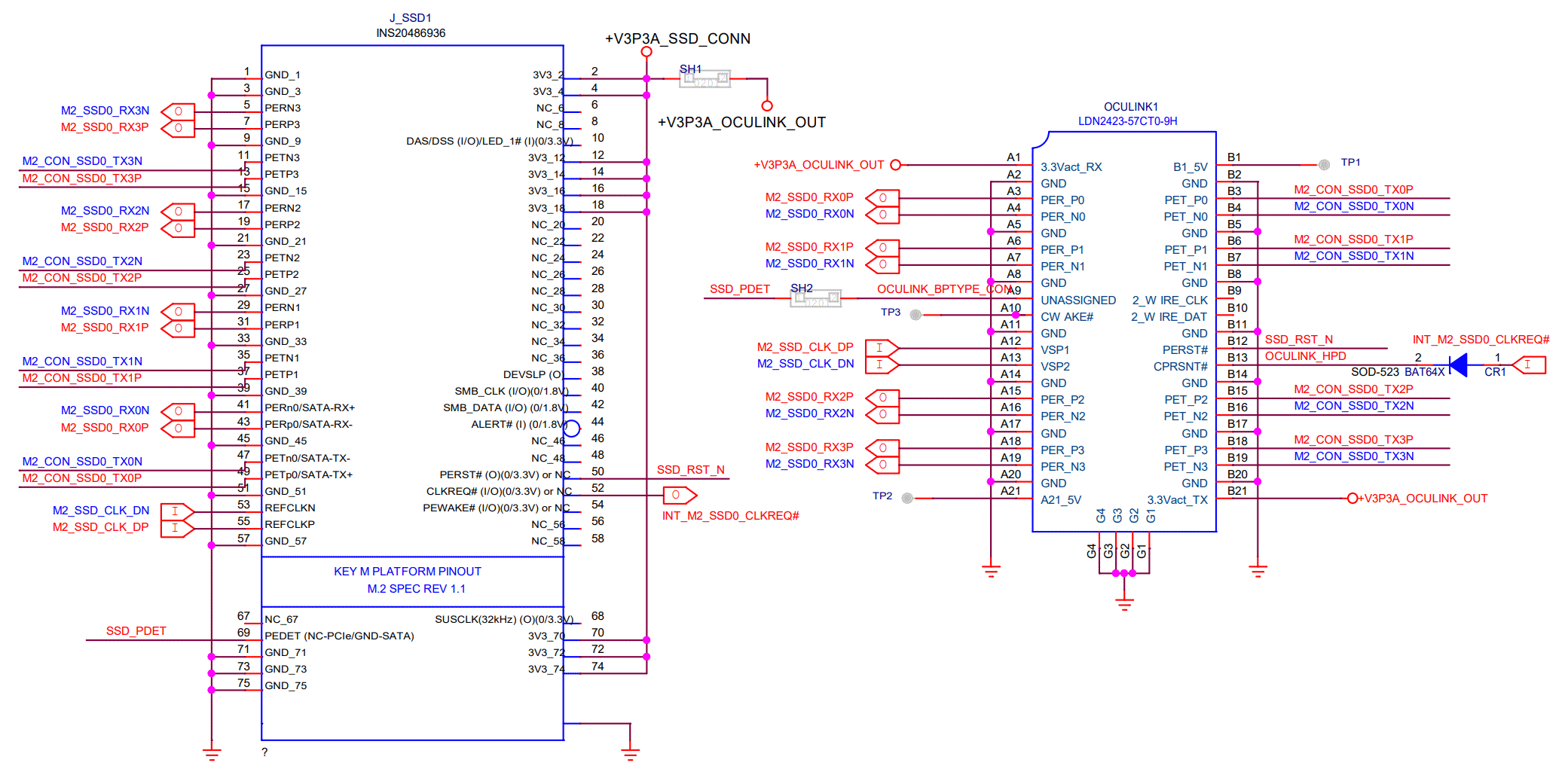

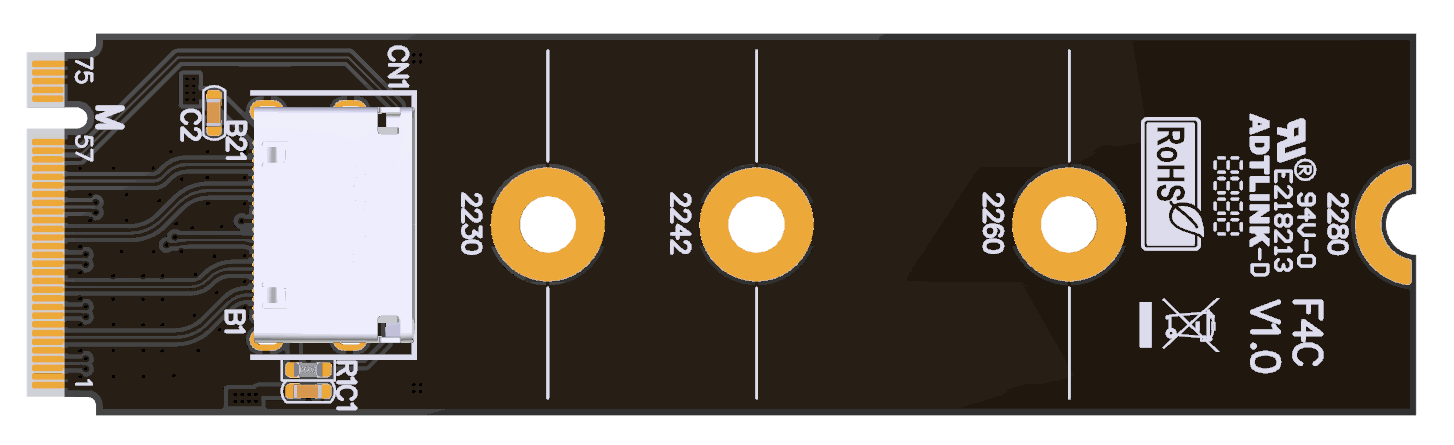

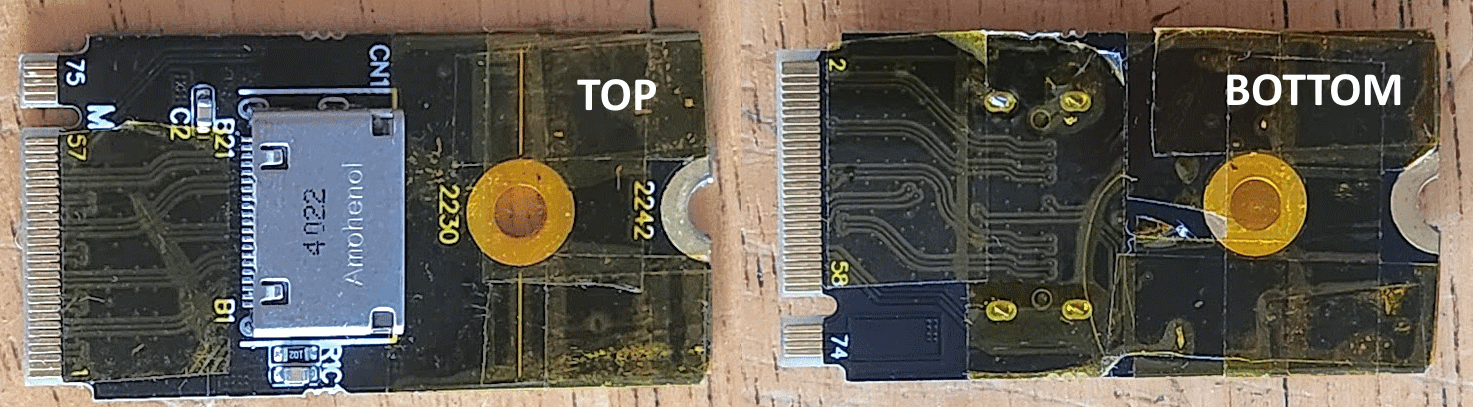

Adtlink M.2 to Oculink card

Image 4. Adtlink F4C M.2 to Oculink adapter card

(source)

Image 5. Purchased Adtlink F4C M.2 to Oculink adapter card with modifications

[PERST, CLKREQ]are connected.[PEWAKE, PEDET]are not connected.[SMB_CLOCK, SMB_DATA]are connected.[MFG_CLOCK, MFG_DATA]are not connected.3.3Vis connected.REFCLKis connected with same polarity.[PERxy, PETxy]lanes are connected with opposite polarity and opposite order.

Summary

PERSTmust be connected.CLKREQmust be connected, possibly through a diode, or shorted to ground on host side.PERSTis optional.PEWAKEis not connected (might be optional?).[SMB_CLOCK, SMB_DATA]are optional.[MFG_CLOCK, MFG_DATA]are not connected.3.3Vis connected.REFCLKmust be connected with same polarity.[PERxy, PETxy]can be connected in opposite polarity and/or opposite order.